Introducción

Cuando se habla de circuitos inversores, también llamados puentes inversores por [1], [2] los define como sistemas que funcionan automáticamente sin necesidad de estar conectados a ninguna red alterna, de forma que permiten transformar corriente continua a alterna. Agregando a lo anterior, [3] aclara que son circuitos que transfieren potencia desde una fuente continua a una carga de corriente alterna y les define aplicaciones como motores de corriente alterna de velocidad ajustable, sistemas de alimentación interrumpida (SAI) y dispositivos de corriente alterna que funcionan a partir de una batería móvil.

Es, por cuanto, imperativo definir un modelo circuital básico que sirva como referencia para el diseño de inversores de una manera simple, completa y adaptable a las distintas necesidades del diseñador. A continuación, se detallará una propuesta de inversor trifásico separada en tres etapas, facilitando así la adaptabilidad del diseño a las distintas situaciones que se puedan presentar, y utilizando como parámetro una onda de siete niveles.

Para efectos de este artículo, se define un nivel como una señal de tensión constante de corta duración, de modo que al aumentar o disminuir el valor de tensión del nivel se forma una onda senoidal de apariencia escalonada (ver figura 3). De este modo, se pretende desarrollar un circuito modelo para un inversor trifásico de siete niveles, que implica individualmente el diseño de un circuito de generación de onda monofásica, uno de control y uno de desfase, que sean compatibles entre sí.

Marco metodológico

[2] y [4], proponen un circuito base como se muestra en la Figura 1. De este modo, al adaptar este modelo a un sistema en cascada asimétrico para cada una de las secciones de disparo es posible generar una onda de siete niveles partiendo de ocho tiristores por fase (ver Figura 1).

Teniendo en cuenta lo anterior, es vital una etapa de control que genere una secuencia de disparo correcta en los tiristores y de esta manera se cree la onda buscada. Finalmente, se debe tener en cuenta que se está buscando una señal trifásica de salida, por lo que se necesita una etapa que genere las tres ondas con su desfase correspondiente, en este caso 120°, pero este valor puede ajustarse a gusto del diseñador. Por lo tanto, el circuito total estará conformado por tres etapas: etapa de control, etapa de generación de onda y etapa de desfase.

Etapa de generación de onda monofásica

Para el circuito planteado, se propone crear tres circuitos idénticos para cada una de las ondas de salida, con una etapa de control idéntica pero que será desfasada temporalmente por la etapa de desfase. Así, se plantea un circuito en cascada asimétrica (ver Figura 2 y Figura 3) para poder generar una onda de siete niveles utilizando solamente ocho tiristores por fase.

El circuito planteado, en la Figura 2 permite la generación de los escalones presentados en la Figura 3 controlando la trayectoria que sigue la corriente, generando sumas o restas de tensión entre las fuentes de tensión.

Etapa de control

Dado que las compuertas de los tiristores deben controlarse bajo una secuencia periódica, la solución planteada a este problema es la utilización de una máquina de estados sincrónica. De este modo, es necesario definir la secuencia de estados correspondiente (ver Cuadro 1) y partiendo de esta se puede crear la tabla de estados para obtener la función de control de los flip-flops utilizados, en este caso JK (ver Cuadro 2).

Cabe destacar que partiendo de la tabla de estados se generó un mapa de Karnaugh para obtener la función de cada una de las entradas J y K de los flip-flops.

Otro aspecto importante a tener en cuenta con respecto a la máquina de estados es la señal de reloj que controla los cambios de la secuencia. De este modo, es necesario contemplar la frecuencia deseada en la onda de salida y la cantidad de estados en la máquina. En este caso, se tienen 12 estados, por lo tanto, la frecuencia de la señal de reloj ha de ser 12 veces mayor a la frecuencia de la onda de salida del inversor.

Cuadro 1 Secuencia de disparo de compuertas de los tiristores de la figura 2

| Estado | [57]Actual [58] [59] [60] | [61]Siguiente [62] [63] [64] | [65] [66] [67]||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Tensión | [68]S1A | [69]S2A | [70]S1B | [71]S2B | [72]Tensión | [73]S1A | [74]S2A | [75]S1B | [76]S2 B | [77] [78]|

| 0 | [79]0 | [80]0 | [81]0 | [82]0 | [83]0 | [84]-V DC | [85]0 | [86]0 | [87]0 | [88]1 | [89] [90]

| 1 | [91]-VDC | [92]0 | [93]0 | [94]0 | [95]1 | [96]-2VDC | [97]0 | [98]1 | [99]0 | [100]0 | [101] [102]

| 2 | [103]-2VDC | [104]0 | [105]0 | [106]1 | [107]0 | [108]-3VDC | [109]0 | [110]0 | [111]0 | [112]0 | [113] [114]

| 3 | [115]-3VDC | [116]0 | [117]0 | [118]1 | [119]1 | [120]- | [121]- | [122]- | [123]- | [124]- | [125] [126]

| 4 | [127]- | [128]0 | [129]1 | [130]0 | [131]0 | [132]-2V DC | [133]0 | [134]1 | [135]0 | [136]1 | [137] [138]

| 5 | [139]-2VDC | [140]0 | [141]1 | [142]0 | [143]1 | [144]VDC | [145]0 | [146]1 | [147]1 | [148]1 | [149] [150]

| 6 | [151]-VDC | [152]0 | [153]1 | [154]1 | [155]0 | [156]- | [157]- | [158]- | [159]- | [160]- | [161] [162]

| 7 | [163]- | [164]0 | [165]1 | [166]1 | [167]1 | [168]0 | [169]1 | [170]1 | [171]0 | [172]1 | [173] [174]

| 8 | [175]0 | [176]1 | [177]0 | [178]0 | [179]0 | [180]V DC | [181]0 | [182]0 | [183]1 | [184]0 | [185] [186]

| 9 | [187]VDC | [188]1 | [189]0 | [190]0 | [191]1 | [192]- | [193]- | [194]- | [195]- | [196]- | [197] [198]

| 10 | [199]- | [200]1 | [201]0 | [202]1 | [203]0 | [204]2VDC | [205]1 | [206]0 | [207]0 | [208]0 | [209] [210]

| 11 | [211]2VDC | [212]1 | [213]0 | [214]1 | [215]1 | [216]3VDC | [217]1 | [218]0 | [219]1 | [220]0 | [221] [222]

| 12 | [223]3VDC | [224]1 | [225]1 | [226]0 | [227]0 | [228]- | [229]- | [230]- | [231]- | [232]- | [233] [234]

| 13 | [235]- | [236]1 | [237]1 | [238]0 | [239]1 | [240]2V DC | [241]1 | [242]1 | [243]1 | [244]1 | [245] [246]

| 14 | [247]2VDC | [248]1 | [249]1 | [250]1 | [251]0 | [252]VDC | [253]1 | [254]0 | [255]1 | [256]1 | [257] [258]

| 15 | [259]VDC | [260]1 | [261]1 | [262]1 | [263]1 | [264]0 | [265]1 | [266]1 | [267]1 | [268]0 |

Así, se propone utilizar un circuito astable cuya frecuencia está en función de las resistencias y el condensador utilizado (1).

Cuadro 2 Tabla de estados de la máquina de estados propuesta

| Estado | [278]Tensión actual | [279]Tensión siguiente | [280]FF0 [281] | [282]FF1 [283] [284] | [285]FF2 [286] | [287]FF 3 [288] | [289] [290] [291] [292] [293]|||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| J | [294]K | [295]J | [296]K | [297]J | [298]K | [299]J | [300]K | [301] [302]||||

| 0 | [303]0 | [304]-VDC | [305]0 | [306]x | [307]0 | [308]x | [309]0 | [310]x | [311]1 | [312]x | [313] [314]|

| 1 | [315]-VDC | [316]-2VDC | [317]0 | [318]x | [319]1 | [320]x | [321]0 | [322]x | [323]x | [324]1 | [325] [326]|

| 2 | [327]-2VDC | [328]-3VDC | [329]0 | [330]x | [331]0 | [332]x | [333]x | [334]1 | [335]0 | [336]x | [337] [338]|

| 3 | [339]-3VDC | [340]- | [341]x | [342]x | [343]x | [344]x | [345]x | [346]x | [347]x | [348]x | [349] [350]|

| 4 | [351]- | [352]-2VDC | [353]0 | [354]x | [355]x | [356]0 | [357]0 | [358]x | [359]1 | [360]x | [361] [362]|

| 5 | [363]-2VDC | [364]VDC | [365]0 | [366]x | [367]x | [368]0 | [369]1 | [370]x | [371]x | [372]0 | [373] [374]|

| 6 | [375]-VDC | [376]- | [377]x | [378]x | [379]x | [380]x | [381]x | [382]x | [383]x | [384]x | [385] [386]|

| 7 | [387]- | [388]0 | [389]1 | [390]x | [391]x | [392]0 | [393]x | [394]1 | [395]x | [396]0 | [397] [398]|

| 8 | [399]0 | [400]VDC | [401]x | [402]1 | [403]0 | [404]x | [405]1 | [406]x | [407]0 | [408]x | [409] [410]|

| 9 | [411]VDC | [412]- | [413]x | [414]x | [415]x | [416]x | [417]x | [418]x | [419]x | [420]x | [421] [422]|

| 10 | [423]- | [424]2VDC | [425]x | [426]0 | [427]0 | [428]x | [429]x | [430]1 | [431]0 | [432]x | [433] [434]|

| 11 | [435]2VDC | [436]3VDC | [437]x | [438]0 | [439]0 | [440]x | [441]x | [442]0 | [443]x | [444]1 | [445] [446]|

| 12 | [447]3VDC | [448]- | [449]x | [450]x | [451]x | [452]x | [453]1 | [454]x | [455]x | [456]x | [457] [458]|

| 13 | [459]- | [460]2VDC | [461]x | [462]0 | [463]x | [464]0 | [465]1 | [466]x | [467]x | [468]0 | [469] [470]|

| 14 | [471]2VDC | [472]VDC | [473]x | [474]0 | [475]x | [476]1 | [477]x | [478]x | [479]1 | [480]x | [481] [482]|

| 15 | [483]VDC | [484]0 | [485]x | [486]0 | [487]x | [488]0 | [489]x | [490]0 | [491]x | [492]1 | [493] [494]|

| Función [495] [496] | [497]- | [498]- | [499]- | [500]- | [501]- | [502]- | [503]- | [504]- | |||

Etapa de desfase

Diseño de desfasador por monoestables

Como mencionan [2] y [5], para evitar pérdidas de potencia en el sistema, así como eventuales fluctuaciones de tensión y corriente en las líneas, es recomendable crear un circuito para cada fase. De este modo, es necesario desarrollar un retraso entre los circuitos de cada fase.

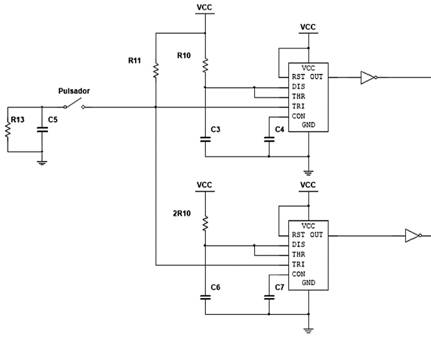

Para esto, se propone utilizar un circuito monoestable con salida en lógica negada que alimente la entrada “reset” de los flip-flops de la segunda y tercera fase (ver Figura 4). Así, al presionar el pulsador, se generará un pulso que reiniciará la secuencia de la máquina de estados asociada estas fases pasado un tiempo determinado (2).

Un aspecto importante a tener en cuenta es que el tiempo que el pulsador permanezca presionado influye indirectamente en el tiempo de retraso, por lo tanto, para evitar que este efecto altere el retraso, entre el pulsador y la referencia se colocó un circuito RC.

Diseño de desfasador por circuito RC

Si se tiene en cuenta la premisa que, partiendo de una serie de circuitos desfasadores es posible obtener una serie de ondas de salida, con forma y amplitud similar, pero con una separación de 120° entre ellas, [6] propone un modelo que parte de un circuito desfasador RC básico (ver Figura 5), y a través del cual, en teoría, es posible obtener el resultado de tres ondas similares.

Si se parte del diagrama fasorial del circuito de la figura anterior (Figura 6), se tiene que la magnitud de la tensión de alimentación en el primario del transformador será el doble que la de la tensión del nodo entre la derivación central del transformador y el nodo entre la resistencia y el condensador, pero con un desfase que se obtiene geométricamente de la Figura 6. Por lo tanto, la relación de vueltas del transformador debe ser de 2:1.

De la misma manera, el ángulo comprendido entre VS y VBN será el suplemento del ángulo de desfase entre la señal de VS y VBN. Así, teniendo en cuenta que la magnitud de VS es la misma de VAn y VBn, el ángulo entre VC y VR es recto, al aplicar distintas razones trigonométricas y llamar φ al ángulo entre VS y Van y θ al ángulo de fase entre las señales de VS VBN se tendría que:

Análisis de resultados

Un aspecto importante a tener en cuenta tras el diseño del circuito es que inicialmente se escogieron tiristores para la etapa de generación de onda monofásica, no obstante, puede utilizarse cualquier tipo de transistor para esta labor, siempre y cuando la etapa de control se adecúe a las características de funcionamiento de este.

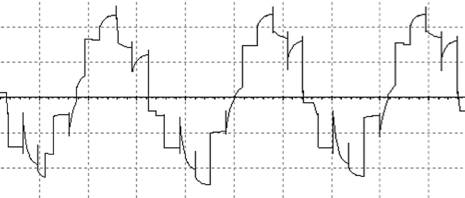

Ahora, asumiendo un comportamiento ideal en los tiristores de la etapa de generación de onda monofásica, la onda de salida será la planteada por [5] (ver Figura 3.) Empero, se debe tener en cuenta que los dispositivos reales no se comportan de manera ideal, así, al utilizar un tiristor no ideal en la simulación es de esperar un comportamiento rudimentariamente senoidal (ver Figura 7).

De la misma manera, al analizar las propuestas para la etapa de desfase, al utilizar el circuito desfasador RC se debe contemplar el efecto de campo que se da en los transformadores, como menciona [6]. Dado que estos son bobinas tienen una inductancia propia que se opone a un cambio brusco en la corriente, así, teniendo en cuenta que los cambios escalonados tienen una amplia separación entre ellos al utilizar siete niveles, se generarán picos de alta tensión (ver Figura 8).

El efecto anterior no solo genera altas distorsiones amónicas en el sistema, sino que tienen una gran posibilidad de dañar los dispositivos utilizados en la etapa de generación de onda monofásica.

Por otra parte, al analizar la eficiencia del sistema, al comparar las etapas de desfase, se tiene que si bien el circuito de desfase RC consume una tercera parte de la potencia, es de esperar que entregue menos de un tercio de lo que entregaría su contraparte, empero, teniendo en cuenta que la tensión que alimenta la segunda (fase B) y tercera (fase C) fase se mide entre la derivación central del transformador y el nodo de unión de dos elementos, se da una pérdida aún mayor, disminuyendo considerablemente la tensión de salida en estas fases.

De este modo, si bien se puede modificar la relación de vueltas de los transformadores para poder alcanzar una amplitud uniforme entre las tres fases, la potencia entregada individualmente decaerá considerablemente de fase a fase.

Continuando, al analizar la precisión con la que se puede obtener el desfase deseado entre las fases, el circuito desfasador por monoestable presenta una desventaja, ya que a pesar de que es posible variar el ángulo de fase entre las fases variando la resistencia de carga del condensador o utilizando un potenciómetro, debe presionarse el pulsador al realizar cada cambio y ver las ondas de salida, impidiéndose así realizar el cambio fino en tiempo real. Por su parte al variar la resistencia en el circuito RC se da un cambio inmediato en el ángulo entre las fases.

Al analizar las ventajas y desventajas de las etapas de desfase planteadas, es posible determinar que, para efectos prácticos, el circuito desfasador por monoestables es más efectivo para la entrega de potencia a cargas trifásicas, dado que permite una entrega de mayor cantidad de potencia que el circuito desfasador RC. Además, permite el uso de dispositivos más comunes y baratos, ya que no deben estar adecuados contra el efecto de campo, como transistores y MOSFETs.

No obstante, para efectos demostrativos, es posible utilizar el circuito desfasador RC, ya que permite realizar un cambio inmediato en la separación de las fases, además que es más sencillo de analizar, no obstante, requiere dispositivos específicos que deben estar adecuados contra efecto de campo y debe operarse en baja tensión.

Conclusiones

Dados los resultados obtenidos en las simulaciones, se puede demostrar que, partiendo de una máquina de estados finitos con flip-flop JK es posible crear un circuito inversor monofásico, y que, al agregar una etapa desfasadora, es posible obtener un inversor trifásico. Por su parte, los circuitos desfasadores utilizados presentan diferentes comportamientos: el circuito desfasador por monoestables presenta una lógica más compleja, ya que es necesario crear individualmente etapas monofásicas, pero da un resultado de forma idéntico en las tres ondas.

El circuito desfasador RC, por su parte, además de aumentar el consumo de potencia en los elementos de diseño, tiende a alterar la onda, ya que funciona además como un filtro, que, si bien permite suavizar el contorno de la onda, también tiene efectos de atenuación. De este modo, se considera más efectivo el desfase por monoestables por la uniformidad en la señal de salida.

Recomendaciones

El modelo propuesto presenta individualmente circuitos poco complejos, que permite adaptarlo fácilmente a las distintas necesidades de los diseñadores, no obstante, la onda de salida podría mejorarse aumentando el número de niveles en la etapa de generación monofásica. Además, el uso de filtros a la salida del sistema permitiría obtener una onda más suave.